作者 Wolfe Yu

前言

ADC在实际应用中,经常会出现无法达到标称精度的情况,而且还会出现波形严重失真的问题,这一现象长期困扰着我们的硬件工程师,那么,在实际的ADC应用中,为何会出现这种情况呢?

笔者在这里通过一个实例和大家一起共同来探讨 ADC在应用中可能会碰到的问题。

案例分享

日前,有客户公司在用某ADC做AD转换的时候,碰到这样一个问题,客户传感器型号PT100,在采集信号时,输入采样端的波形如下:

我们首先假定这是一个直流前端,抛开交流耦合等因素,单从这个采样波形来看,采样端明显是工作异常的。那么,为何会出现这种情况呢?

ADC模型初探

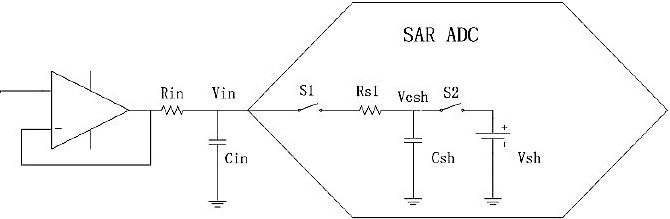

我们先来大致解剖一下 ADC电路参考模型及其驱动电路,通过这个模型来跟大家共同来探讨一番,为了便于做定量分析,我们在文中插入一些公式,供大家参考。

为了更加直观,我们删繁就简,重新整理这个电路,单看输入、采样端的电路模型,大致如下:

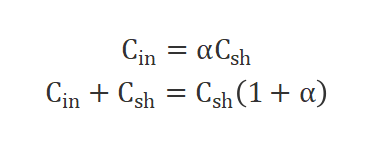

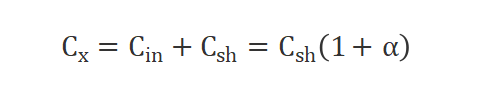

为了简化设计,我们假设输入电压近似于一个直流电源,抛开耦合因素,输入内阻远大于采样电阻,Rin>>Rsh,输入电容和采样电容之间的关系用a来表示:

初始状态,相对来说Vin向Cin充电相对较小,主要看Cin向Csh充电过程,我们构建电路模型如下图所示:

根据以上模型,可以大致推导出第1阶段输入电压和采样电压对应方程,以及采样电容充电时间关系。

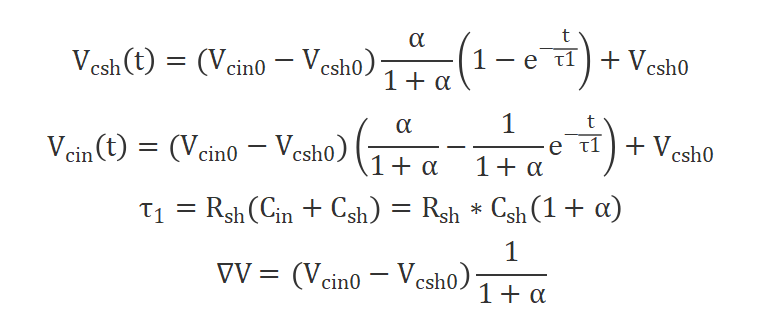

当Csh电压迅速上升到与Cin相当之后,我们忽略Rsh对电路的影响,我们重新构建第2阶段电路模型如下。

此时,等效电容为输入电容和采样电容并联,根据以上模型,可以大致推导出输入电压和采样电压对应方程如下:

此时,根据等效模型,我们可以推导出正常状态下:

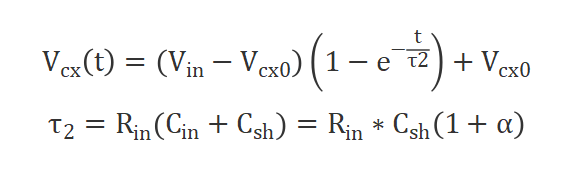

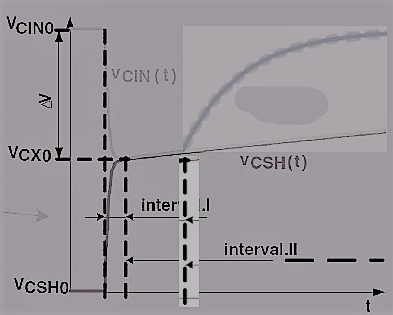

由此,我们可以画出采样端波形大致如下:

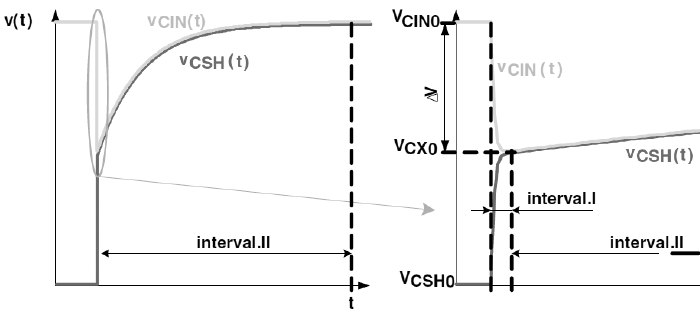

根据ADC内部结构和,我们可以很轻松的推导出,第二阶段的时间远远大于第一阶段的时间,同时,我们也可以推导出,采样时间和输入电阻必须满足:

按照正常采样,第二阶段采样时间必须要满足输入电阻、输入电容和采样电容并联的乘积关系。如果采样不足,又会出现怎样的情况呢?在采样开关断开之后,采样保持阶段,由于Cx变小,输入电容充电速度明显加快,此时,Csh电压几乎不变,大致波形应如下(具体推导公式不再列出):

结合该客户反馈的测试结果,我们大致判断出,客户这个问题是由于在未达到采样条件时就开始进行ADC采样并转换引起。

解决方案

结合上述电路模型及其推导公式,我们该如何解决此类问题呢?我们给出三种建议:

A. 延迟采样时间;

B. 加大输入电容;

C. 增加驱动电路,重构输入阻抗。

实施细节

一、延迟采样,增加采样周期

这一点不难理解,只要采样速率没有要求,理论上来说,增加采样周期,完成ADC转换完全没问题,本文不做重点讲解。

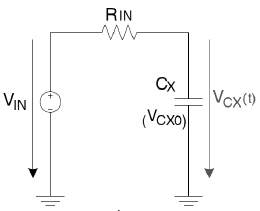

二、加大输入电容

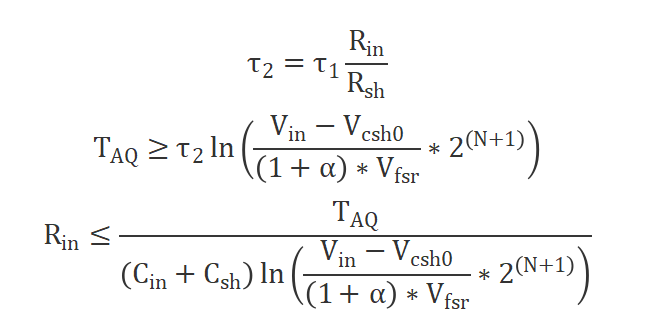

我们在很多ADC采样场合都看到ADC输入前端有一个电容,如果我们设定Rin非常小,忽略不计,那么这个电容有何作用呢?本文中,我们有一个推导公式:

由于在每个采样周期内,输入电容和采样电容的电压值都会相对固定,如果我们通过调整输入输入电容和采样电容的比值来调整第一阶段的快速充电时间,这似乎不失为一个好办法。

但是,当输入电源发生变化的时候,由于采样电容吸收能力有限,采样端输入电容泄放又会遇到新的难题。同时,对于高频信号来说,电容越大,等效阻抗会更小。

所以,在采样端引入输入电容的时候,我们需要非常谨慎,这个电容大多数是用来做高频分量滤波用的。

三、增加驱动能力,重构输入阻抗

我们再回到第2阶段采样时间这个公式:

如果我们能够降低输入阻抗,就会大大缩短采样时间,目前增加驱动有两种主流方法:

第一种是用变压器来做驱动电路,这个方法有一个弱点,只能针对交流信号,对工作频率有要求,需要做匹配设计。

另一种方法是用运放做跟随器,这样可以大大降低信号端的内阻,大多数模拟前端都采用这种方法来做前端设计。

经过和客户确认,客户后来采用运放做跟随驱动的方法,重新测试一版,测试采样端波形如下图,从硬件电路来看,应该找到问题所在,目前还在验证中。

Microchip ADC介绍

针对传感器市场,Microchip推出多种Delta-Sigma ADC,可以满足多种不同应用需求,特别是这么缺货的年代,

MCP356X简介:

24 bits Delta-Sigma ADC

153.6 kSPS @ 16 bits,19.2 kSPS @ 24 bits

OSR Rang:32-98034

VREF External VREF rang:0.1V-AVDD

Clock Internal or External

RMS Effective Resolution: Up to 23.3 bits

Power Consumption:0.8-2 Ma

Package:UQFN-20

同时,Microchip也有多种运算放大器可以用来做前端设计,供大家选择。